(Frequenz-) Teiler

ANALOGES FLIRT

Allgemeines

Der Frequenzteiler soll die Frequenz des

Oszillators, der mit einer Frequenz von 33 kHz schwingt, durch den Faktor 10

teilen. Somit sollten wir eine Frequenz von 3.3 kHz erhalten.

Diese Frequenz wird dann für die Modulation

verwendet..

Der Frequenzteiler besteht im wesentlichen aus einem NAND – Gatter, einem Counter, einem Toggle Flip Flop, und damit wir ein Signal ohne DC – Anteil bekommen, gehört noch ein Hochpass dazu, der eine Grenzfrequenz von einigen Hz hat.

Die Anordnung der einzelnen

Elemente kann man an dem nachstehenden Blockschaltbild erkennen.

Das Signal vom Oszillator

Das Signal, das vom Oszillator geliefert

wird, sollte einem Sinus mit 33 kHz entsprechen.

Durch die Realisierung des Oszillators mit

einem Quarz sollten keine Oberwellen vorhanden sein.

Das Oszillatorsignal muss einen Offset von

2.5 V haben und eine Amplitude von mindestens 4 Vss, damit die anschließende

Logikschaltung sauber schaltet.

Allgemeines

zur Logik

Ich verwende für den gesamten Teiler eine

CMOS – Logik. Dadurch benötige ich nur eine Versorgungsspannung von 5 Volt und

Masse (GND).

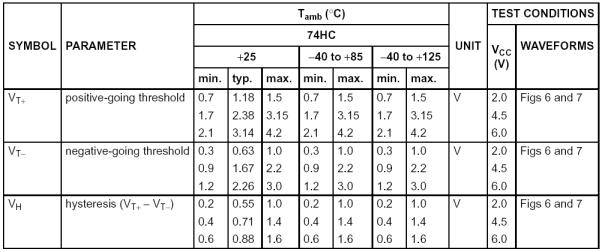

Auszug aus dem Datenblatt des NAND – Gatters

74HCT132 mit Schmittriggereingang

Aus dieser Tabelle des 74HCT132 kann man die

Pegel ablesen, die benötigt, werden um ein eindeutiges LOW bzw. HIGH zu

erkennen.

Da wir eine Versorgungsspannung von 5V haben,

nehmen wir den Mittelwert von 4.5V und 6V.

Ich beziehe mich jetzt auf die typischen

Werte bei 5V.

Ein LOW wird erkannt, solange die

Eingangsspannung nicht größer als

ist.

ist.

Ein HIGH wird erkannt, sobald die

Eingangsspannung größer als

ist.

ist.

Die

Spannungsversorgung

Da wir nur eine

Versorgungsspannung von 12 Volt haben, realisierte ich einen Spannungsregler

mit einer Zenerdiode und einem Widerstand.

Da wir nur eine

Versorgungsspannung von 12 Volt haben, realisierte ich einen Spannungsregler

mit einer Zenerdiode und einem Widerstand.

Die Zenerdiode hat eine Zenerspannung von 5.2

Volt.

Der Widerstand R38 ist für die

Strombegrenzung zuständig.

Da die Logik nur sehr wenig Strom aufnimmt

und die Spannung durch die Zenerdiode stabil gehalten wird, kann ein Widerstand

von 1.5 k eingesetzt werden.

Dies ergibt einen Leerlaufstrom (wenn keine

Logik angeschlossen ist) von

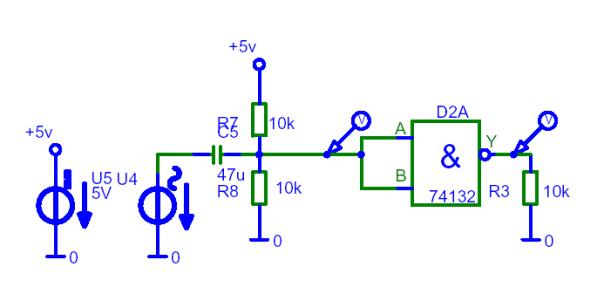

Das

NAND – Gatter

Das Oszillatorsignal wird zuerst auf ein NAND

– Gatter mit Schmittriggereingang geschaltet, um eine Rechteckform zu bekommen.

Bei meiner Schaltung werden die zwei Eingänge

miteinander verbunden und auf das Oszillatorsignal geschaltet.

Da unser Signal ein Sinus mit einem Offset

von 2.5 Volt ist und wir einen Schmittriggereingang haben, bekommen wir ein

Signal, das kein Tastverhältnis von 1:1 hat.

Nach dem NAND – Gatter haben wir einen CMOS –

Pegel.

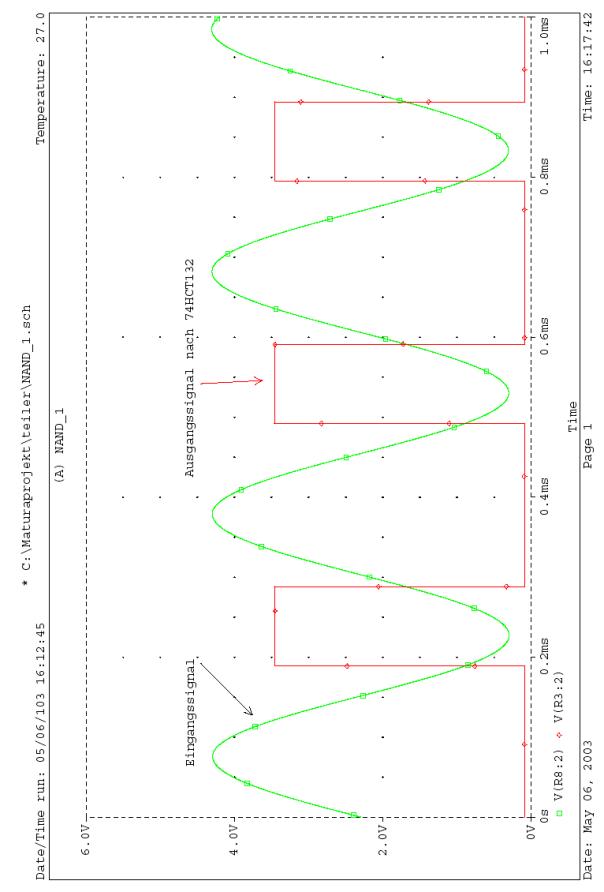

Simulation

des NAND – Gatters

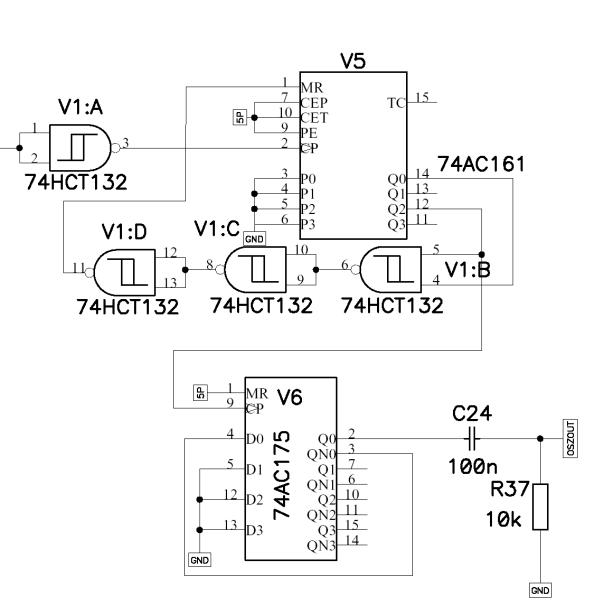

Der Counter

Der Counter übernimmt die Teilung der Frequenz. Bei jedem 5. Impuls am Eingang erreicht er den binären Zustand „0101“ = 5 dezimal.

Der Counter zählt nicht auf 10, da das nachfolgende Toggle Flip Flop noch eine Teilung der Frequenz mit dem Faktor 2 vornimmt.

Der Counter 74AC161 reagiert

auf die positive Flanke, wenn CEP, CET und !PE (PE negiert) auf +5V geschaltet

sind.

Die Kanäle P0, P1, P2 und P3

lege ich auf Masse, da diese in unserer Schaltung nicht benötigt werden.

Ansonsten könnte man einen Anfangszustand auf den Counter geben, der mit

D – Flip Flops realisiert

ist.

Das Rechtecksignal vom

74HCT132 (NAND – Gatter) wird auf den Clockeingang (CP) des Counters geschaltet

und zählt mit jeder positiven Flanke ein Bit aufwärts. Der Zustand des Counters

ist an den Ausgängen Q0, Q1, Q2 und Q3 ersichtlich.

Der RESET (!MR) wird aktiv,

wenn eine logische 0 anliegt. Da wir noch ein NAND – Gatter zur Verfügung haben

und ein AND – Gatter für die Zustandsanzeige benötigen würde, wird das AND

durch ein NAND ersetzt, da es am Ausgang des Teilers nicht wichtig ist, ob eine

logische „0“ oder eine logische „1“ vorhanden ist. Somit kann der RESET direkt auf den Ausgang des 74HCT132, der

nach dem Counter geschaltet ist, geführt werden. Da wir ein Problem mit den

Laufzeiten festgestellt haben, werden die 2 zusätzlichen NAND – Gatter auch

noch in Reihe geschaltet, um die Funktion des NAND – Gatters am Counterausgang

beizubehalten und die Verzögerungszeit des RESET – Impulses zu verlängern.

D. h. liegt am

Counterausgang der Wert „0101“, so wird der Ausgang des 74HCT132 „0“.

Dies aktiviert den RESET und

der Counter fängt von 0 („0000“) an zu zählen.

Liegt stattdessen kein

„0101“ am Ausgang des Counters, so ist der Ausgang des 74HCT132 auf logisch „1“

und der RESET ist nicht aktiv.

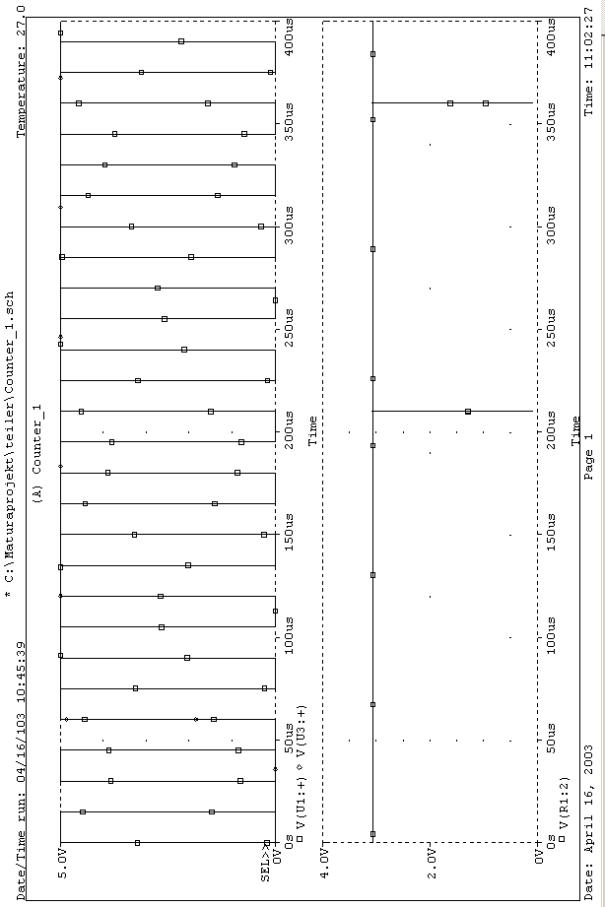

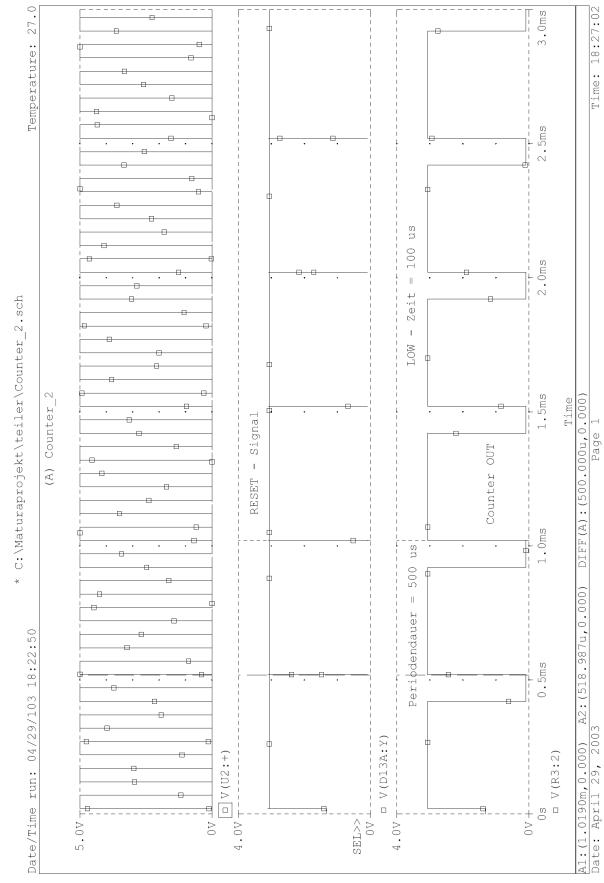

Simulation des Counters

incl. Einem NAND – Gatter am Ausgang

Die Impulsquelle U3 wird zum

Reseten des Counters bei der ersten Periode verwendet.

Der Impuls ist 60 us auf „0“

und schaltet dann auf „1“, wobei er diesen Wert beibehält.

Das AND – Gatter verknüpft

die Impulsquelle U3 und der Ausgang des 74HCT132, damit der RESET geschaltet

werden kann, wenn U3 auf „0“, bzw. wenn

Ausgang des 74HCT132 auf „0“ ist.

Da U3 nach 60 us auf „1“

ist, kommt es nur noch auf den Zustand des 74HCT132 an.

Die Impulsquelle U1 liefert

einen Impuls mit einer Periodendauer von 30 us (33 kHz) und einer

Rechteckamplitude von 0V und 5V.

An der Simulation kann man

erkennen, dass nur ein kurzer Impuls am Ausgang des 74HCT132 ansteht, wenn der

Counter den Wert „0101“ erreicht.

In der Praxis ist der Impuls

breiter, gleicht einem Rechteck, da das NAND – Gatter eine Verzögerungszeit

beim Umschalten von HIGH zu LOW von ca. 4.5 ns besitzt.

Diese Verzögerungszeit ist

für die weitere Logik (bei der Simulation) eindeutig zu erkennen, da z. B der

74HC175 eine maximale Frequenz von ca. 214 MHz besitzt (min. 187 MHz).

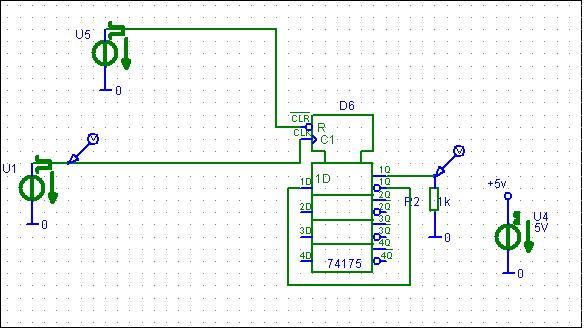

Das Toggle Flip Flop

Das Toggle Flip Flop hat in

meiner Schaltung die wesentliche Funktion der

Frequenzteilung durch den

Faktor 2.

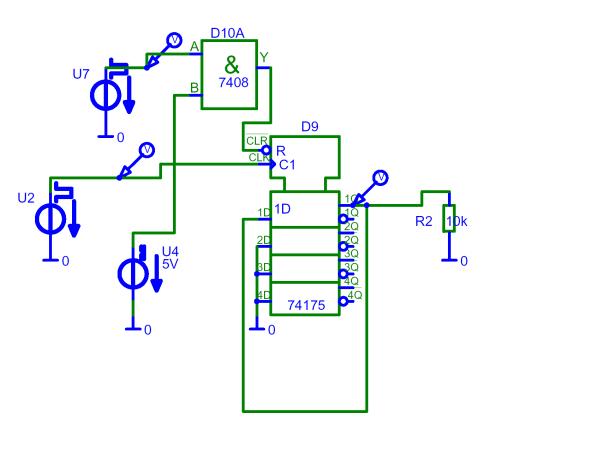

Das Toggle Flip Flop ist

durch ein D – Flip Flop realisiert, wobei der D – Eingang mit dem negierten Q –

Ausgang verbunden wird. Der Clock Eingang des D – Flip Flops wird auf den

Ausgang des 74HCT132 geschaltet, das nach dem Counter geschaltet ist.

Das D – Flip Flop hat eine

maximale Frequenz von 165 MHz. Die Hold Time liegt bei 6 ns.

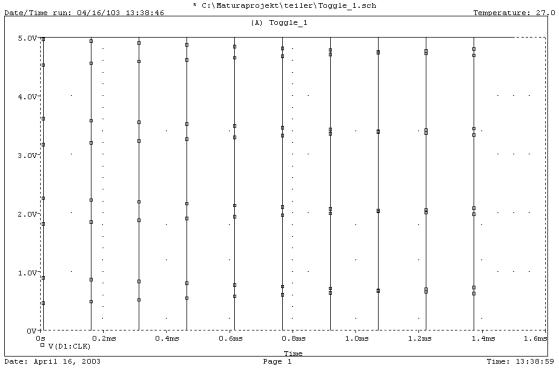

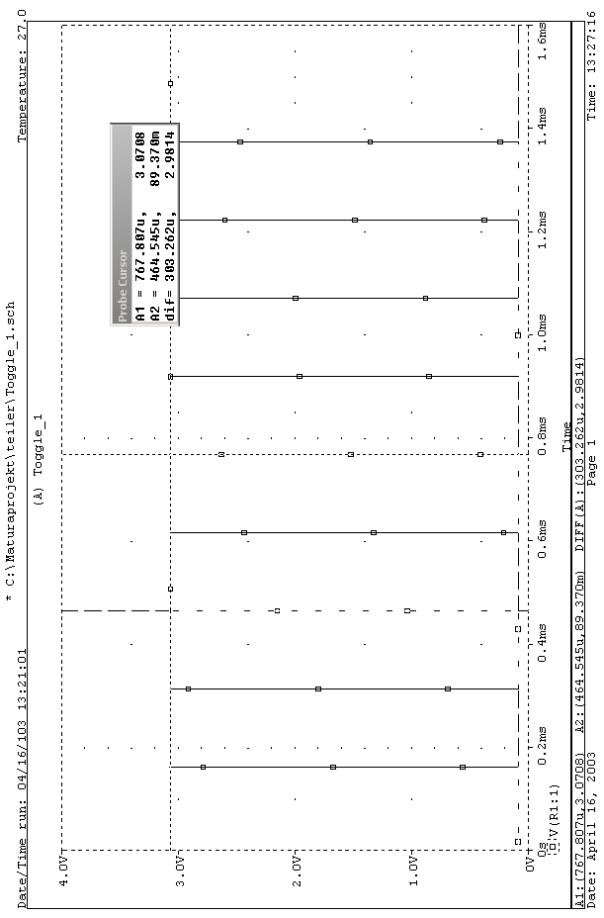

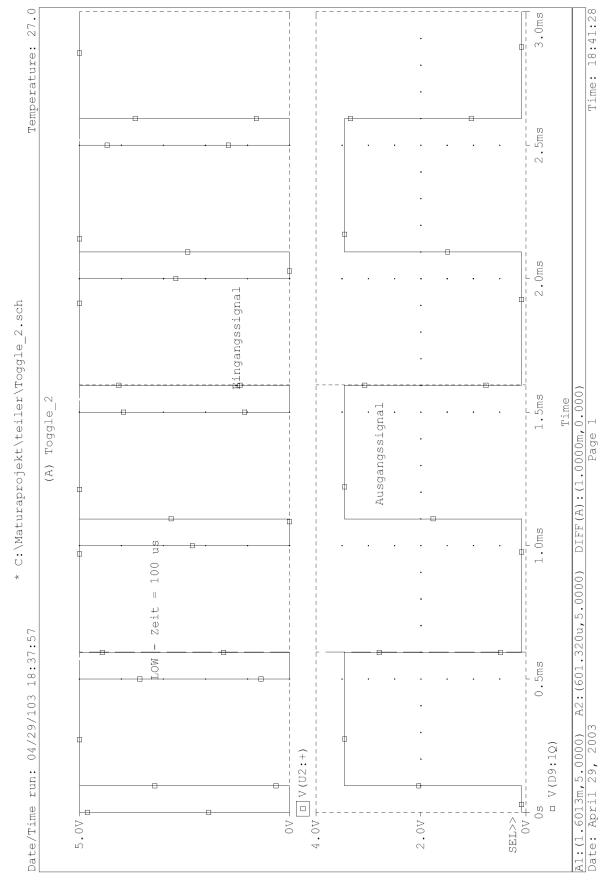

Simulation des Toggle Flip Flops

Als Eingangsimpuls verwende

ich die Counter Testschaltung.

Impulsquelle U1 mit Frequenz

f = 6.6 kHz und Amplitude 5V.

Die Pulsweite ist 1ns.

Diese Grafik enthält das Verhalten der

Impulsquelle U1.

Sandholzer Markus

Hier kann man recht deutlich erkennen, dass nur sehr

schmale Impulse am Clock – Eingang auftreten.

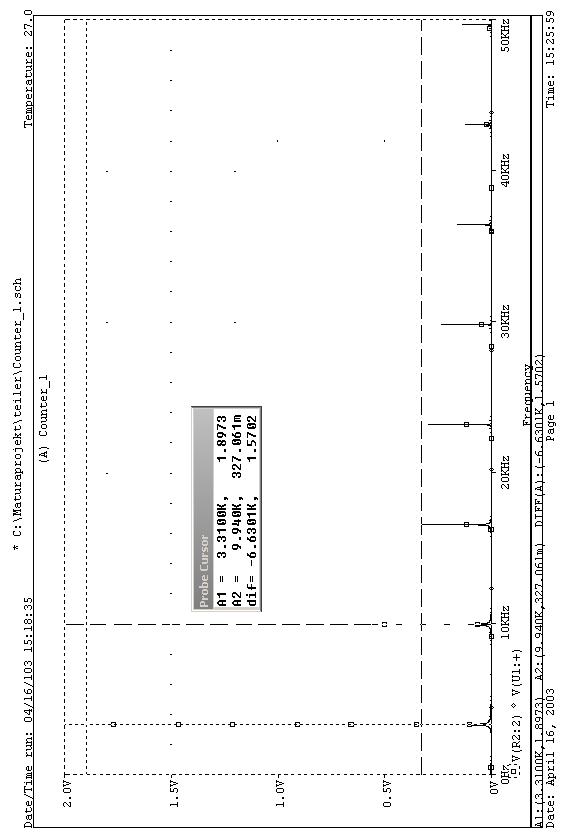

Der Hochpass

Der Hochpass blockiert die Gleichspannung

vor dem Multiplizierer ab.

So erhalten wir ein

erdsymmetrisches Signal ohne Offset mit einer Frequenz von 3.3 kHz und einer

Amplitude von 5 Vss. Da bei einem Rechteck Oberwellen mit ungeradzahligen

Vielfachen auftreten (3 * 3.3 kHz, 5 * 3.3 kHz,...), ergeben sich nach dem

Modulator verschiedenste Mischprodukte. Aus diesem Grund benötigen wir nach dem

Modulator noch einen Tiefpass.

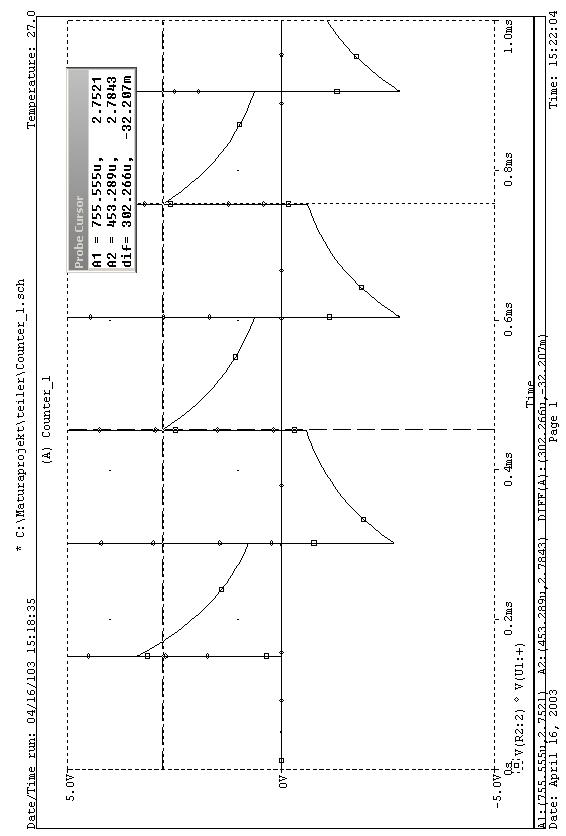

Aufbau des Hochpasses

Schaltung zur Simulation des Hochpasses

Als Eingangssignal habe ich das Signal aus

dem Toggle Flip Flop verwendet.

Hochpass

Eingangssignal

des Hochpasses

Ausgangssignal

des Hochpasses im Zeitbereich

Ausgangssignal

des Hochpasses im Frequenzbereich (mittels FFT)

Die Realität

Nach der Berechnung und Simulation haben wir

die Logik aufgebaut und festgestellt, dass der Ausgangsimpuls des Counters

nicht lang genug ist, damit das Toggle – Flip – Flop reagieren kann.

Somit musste ich eine neue Schaltung finden,

die die gleichen Eigenschaften wie die vorherige Schaltung hat.

Ich entschied mich eine neue Logik zu

entwickeln, ohne neue Bauelemente zu benötigen.

Ich bemerkte, dass das Signal auf das Toggle

– Flip Flop geschaltet werden kann, ohne die Eigenschaften des RESETs zu

ändern, wenn der Zustand „0100“ am Counter anliegt,.

Resultat ist, dass der Impulse am Toggle –

Flip Flop eine Periode länger anliegt.

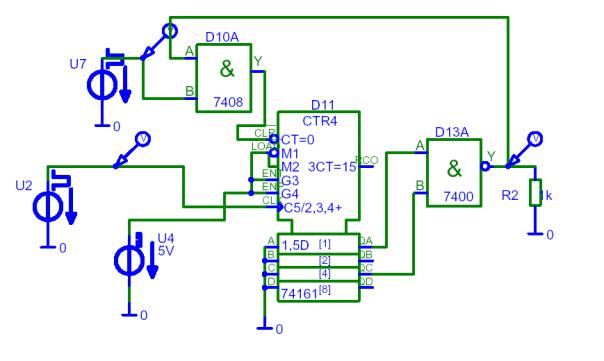

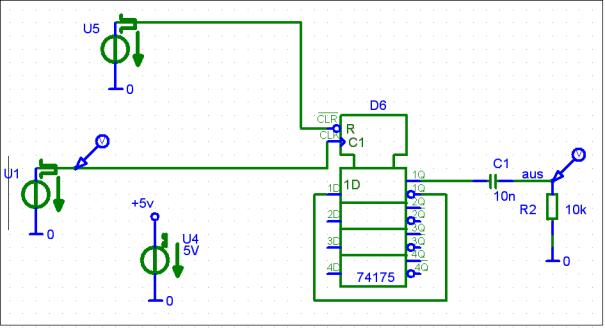

Die Simulation

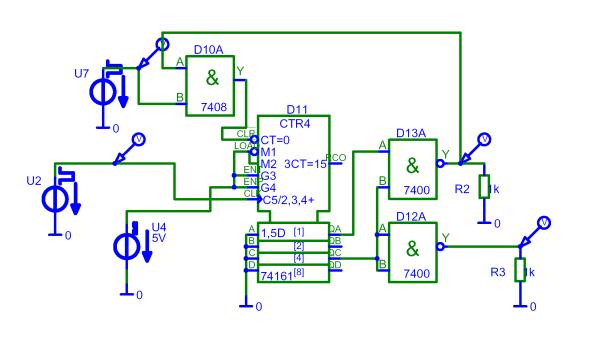

Zur Simulation des Counters wird folgende

Schaltung verwendet. Als Clocksignal wird ein Rechteckimpuls mit 10 kHz

verwendet, damit die Graphen leichter veranschaulicht werden können.

Wie man hier erkennen kann, wird nur noch ein zusätzliches NAND – Gatter benötigt, das im QUAD NAND bisher nicht verwendet wurde.

Nach dem NAND – Gatter D12 wird das Toggle – Flip Flop geschaltet, während das

NAND – Gatter D13 für den RESET zuständig ist.

Das AND – Gatter wird wiederum benötigt, um den Counter zu reseten.

Wie man sieht, hat sich beim Toggle – Flip Flop nichts geändert.

Da ich nur eine Schülerversion von PSpice besitze, musste ich die Logik in zwei Teile aufteilen, da die Schülerversion nur eine Logik mit 3 logischen Bauelementen zulässt.

Der CLOCK wird hier über U2 eingespeist, wobei der zeitliche Verlauf dem Ausgang des NAND – Gatters entspricht.

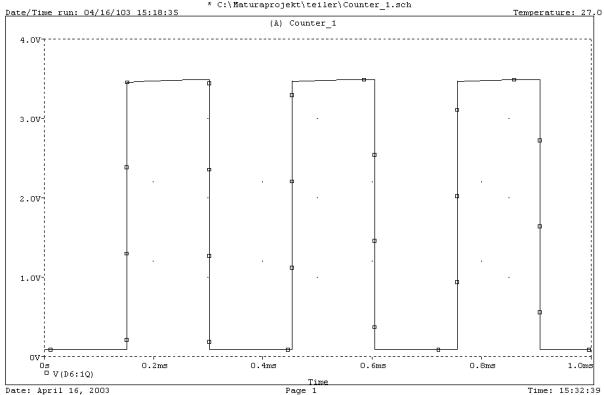

Simulation der

Logikschaltung

An diesen Graphen kann man erkennen, dass sich eine Teilung durch 10 ergibt.

Das heißt, aus einem Signal mit der Frequenz f = 10 kHz (T = 0.1 ms) wird ein Signal mit einer Frequenz von f = 1 kHz (T = 1 ms).

Der positive Impuls am Eingang des Toggle – Flip Flops hat eine Dauer von 400 us.

Diese Dauer reicht, um das Flip Flop zu schalten.

In der Praxis funktioniert diese Schaltung einwandfrei und wird somit beibehalten.

Gesamtschaltung